获奖情况

美国西部时间2024年3月4日,我司与北大合作团队在FPGA’24布线加速竞赛中获得优异的成绩。此次比赛由AMD公司组织并在美国加州举办,共历时3个月,来自北京大学、香港中文大学、中国科学技术大学、加拿大奎尔夫大学等40支队伍、遍布15个国家和地区、超过150名选手报名参赛。

赛事现场

经过激烈的角逐,最终有十支队伍成功入围决赛。决赛通过15个隐藏用例的评比,计算出各个队伍的平均分数,并根据最终得分进行排名。AceRoute以优异的成绩获得了该次比赛的第三名。

AceRoute介绍

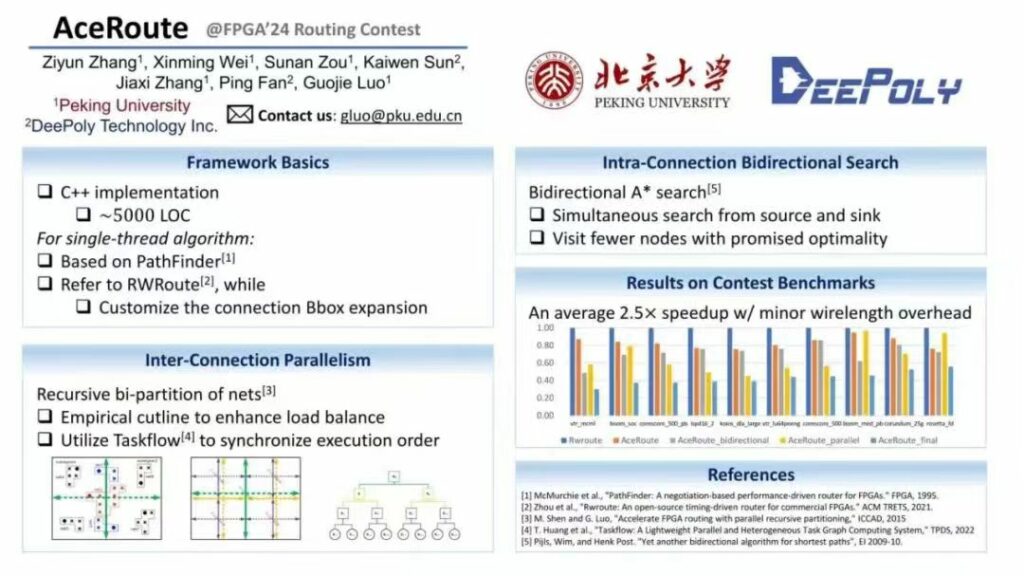

AceRoute基于PathFinder协商布线算法,采用迭代方法消除拥塞并优化其关键路径,参考RWRoute的拥塞代价管理策略,实现高效的C++布线引擎。同时提出自定义的扩展连接边界框的方法,以更好的管理连接并优化布线结果。这些方法的综合应用有助于提高电路性能和可靠性。

Aceroute采用递归网表分割,将网表分割成3到n个平衡子集。根据源和汇位置设计切割线,每次迭代地划分子集,利用任务流确保执行顺序并避免冲突。后期迭代中,动态重新分区以保持负载平衡。

Aceroute在处理内部连接问题时,采用了双向A*算法。这种算法同时从源节点(正向)和汇节点(反向)开始搜索,以寻找最佳路径。这种双向搜索方法在内部连接问题中非常有效,因为它能够减少搜索过程中访问的节点数量,并且能够保证找到的路径是最优的,从而提高了内部连接问题的解决效率。

在竞赛基准测试中,对比AMD/Xilinx研究实验室和比利时根特大学联合研发的高质量布线器RWRoute平均速度提升了2.5倍,而且实现了相同的布线质量。AceRoute同时也成功超越了商业工具Vivado布线器的性能。

赛事介绍

此次参加的研讨会属于FPGA领域三大顶级学术会议之一,该竞赛(Runtime-First FPGA Interchange Routing Contest)由AMD/Xilinx公司发起,美国计算机学会及其会议单位做技术支持,旨在鼓励FPGA布线算法的创新,并促进FPGA交互格式作为与供应商工具互操作的中间格式。

关于深维

北京深维科技有限公司,组建于2016年。公司核心团队由资深专家组成,拥有深厚的EDA学术背景、国内领先的EDA研发能力和丰富的FPGA&SoC开发设计经验,核心成员已获得50余个发明专利,在国际和国内行业顶级刊物发表了数十篇论文。

公司积极响应国家“自主可控”和解决“卡脖子”问题的号召和要求,凭借着在FPGA行业近20年的技术积累和优势资源,推出了面向大容量FPGA的国产正向设计综合工具(组件库)、可靠性设计加固与验证、安全与缺陷检测等工具,已为装备、航天和航空等单位提供定制化EDA解决方案和技术服务。

公司关注客户痛点和致力核心技术攻关,围绕解决大容量FPGA应用开发的设计过程加速和芯片性能优化等问题,为空天、航天、航空、船舶、电力、汽车和通信等行业,提供大容量FPGA设计加速SaaS云服务、定制化FPGA EDA解决方案和技术服务